The abbreviation PCI, short for Peripheral Component Interconnect, succinctly encapsulates its purpose. PCI emerged to address the pressing need for a standardized interface facilitating the connection of peripherals to a PC, capable of accommodating the demanding data transfer rates essential for modern computing tasks such as graphics processing, storage access, networking, and more.

Prior iterations of bus designs suffered from various limitations. Take, for instance, the IBM PC-AT’s standard ISA (Industry Standard Architecture) bus, which could achieve a maximum data transfer rate of 8MB/sec under ideal conditions.

However, real-world performance often fell short of this figure. Factors like the 16-bit data bandwidth and the 24-bit wide address bus compounded the issue, constraining memory-mapped peripherals to the initial 16MB of memory address space. Consequently, the ISA bus gradually needed to be updated in comparison.

More recent advancements, such as IBM’s MCA (Micro Channel Architecture) and the EISA (Extended ISA) bus, boasted improvements such as wider bandwidth (32 bits) and enhanced support for bus mastering and direct memory access (DMA).

However, these upgrades could have provided a substantial leap forward from ISA to offer a sustainable long-term solution. While proposals for faster iterations of both MCA and EISA surfaced, they needed more enthusiasm. Notably, neither option presented a cost-effective solution, a crucial consideration in the fiercely competitive PC market.

Before delving into the technical intricacies, let’s grasp the fundamentals of PCI Express and the basic concepts of PCI.

Evolution and History of PCI

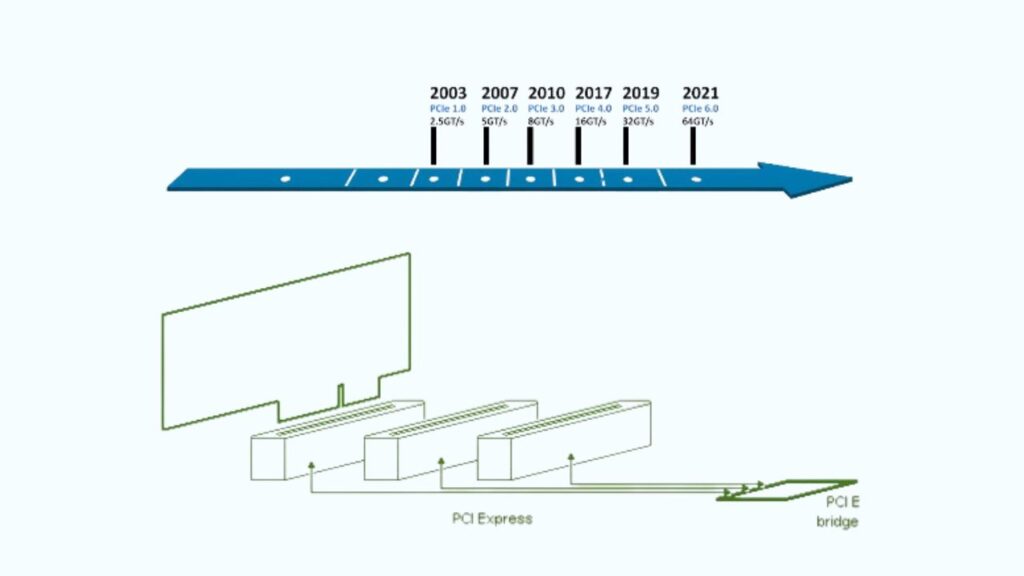

The evolution of PCI into PCI Express is a significant milestone in the world of computing. Originally designed as a standard for connecting peripheral devices to a computer motherboard, PCI has undergone a series of transformations to keep up with the escalating demands of data transfer speeds and efficiency. A compelling comparison can be drawn between PCI and AGP (Accelerated Graphics Port), shedding light on their respective roles in the ever-changing computing landscape.

Technical Aspects of PCI

Understanding PCI entails navigating its standards and specifications. For instance, consider a scenario where a graphics card is communicating with the motherboard. The PCI Standards and PCI Express delineate the parameters within which such devices communicate.

Additionally, the host-to-PCI bridge, acting as a translator, serves as a pivotal component in facilitating seamless data transfer. Moreover, factors such as PCI voltage and timing, which can be compared to the voltage and timing requirements of different electronic devices, contribute to the system’s overall efficiency and compatibility.

Design and Components

The PCI design architecture encompasses various components, each serving a distinct purpose. From the intricate PCI Design to the physical manifestation in the form of a PCI Connector, every element plays a crucial role. Furthermore, the integration of VL-Bus further enhances the capabilities and expandability of PCI-based systems.

Operational Mechanisms

Central to PCI’s functionality are its operational mechanisms governing data transactions. Bus Transactions serve as the backbone of communication between devices, ensuring smooth interoperability.

Additionally, accommodating non-PCI devices within the PCI framework requires meticulous planning and implementation. Moreover, Bus Arbitration mechanisms regulate access to the system bus, optimizing resource utilization.

Understanding Commands

Commands within the PCI framework are the lifeblood that dictates the flow of data and instructions between devices. By categorizing into various Command Types, we streamline the communication process, ensuring efficiency and reliability in data transfer operations. Understanding these commands is key to mastering the intricacies of the PCI framework.

Different width slots Mixing of 32-bit and 64-bit PCI cards

Most 32-bit PCI cards are compatible with 64-bit PCI-X slots, albeit with a caveat. The bus clock rate becomes constrained to the frequency of the slowest card, owing to the shared bus topology inherent in PCI.

For instance, if a PCI 2.3, 66-MHz peripheral is installed into a PCI-X bus capable of 133 MHz, the entire bus backplane operates at 66 MHz. To circumvent this limitation, numerous motherboards incorporate multiple PCI/PCI-X buses. One bus is tailored for high-speed PCI-X peripherals, while another caters to general-purpose peripherals.

Many 64-bit PCI-X cards are engineered to function in 32-bit mode when inserted into shorter 32-bit connectors, albeit with some performance degradation. The Adaptec 29160 64-bit SCSI interface card serves as an example. However, certain 64-bit PCI-X cards are incompatible with standard 32-bit PCI slots.

When installing a 64-bit PCI-X card in a 32-bit slot, the unconnected and protruding 64-bit portion of the card’s edge connector must be considered. No motherboard components must obstruct this overhanging portion of the card edge connector.

FAQs:

What is PCI Express, and how does it differ from traditional PCI?

PCI Express, often abbreviated as PCIe, is an advanced version of the traditional PCI architecture. While both connect peripheral devices to the motherboard, PCIe boasts significant improvements in data transfer rates and efficiency. Unlike traditional PCI, which utilizes a parallel bus architecture, PCIe employs a serial point-to-point connection, allowing for higher speeds and scalability.

How does PCI voltage affect system performance?

PCI voltage plays a crucial role in determining a system’s stability and compatibility. Different devices may require varying voltage levels to operate optimally. Incorrect voltage settings, such as setting a voltage higher than a device can handle, can lead to system instability, malfunctions, or even hardware damage. Adhere to the specified voltage requirements outlined by PCI standards to ensure smooth operation and longevity of components.

What role does the Host to PCI Bridge play in data transfer operations?

The Host to PCI Bridge is a crucial component in the data transfer operations of a system. It acts as a mediator between the CPU (Central Processing Unit) and the peripheral devices connected via PCI. Its primary function is to manage the flow of data between the system’s memory and the connected devices, ensuring efficient data transfer and access. Think of it as a traffic controller, ensuring that data is directed to the right device at the right time. Additionally, the bridge may incorporate features such as DMA (Direct Memory Access) to further enhance data transfer speeds.

Can Non-PCI devices be integrated into a PCI-based system?

Yes, Non-PCI devices can be seamlessly integrated into a PCI-based system through various means such as adapter cards or specialized interfaces. These devices may include legacy hardware or peripherals that do not natively support PCI connectivity.

Adapters or converters enable this integration by translating signals between the device and the PCI bus, allowing for interoperability within the system. This process is similar to using a language translator to communicate with someone who speaks a different language, making it easier to understand and implement.

How do Command Types facilitate efficient data communication within PCI networks?

Command Types within PCI networks dictate the nature of data transactions between devices. By categorizing commands into specific types, such as Memory Read, Memory Write, Configuration Read, and Configuration Write, PCI systems can efficiently manage data flow and address various communication requirements. This classification ensures that data is transferred accurately and promptly, enhancing overall system performance.

Conclusion:

In conclusion, understanding how PCI works is not just a matter of curiosity but a necessity for anyone dealing with modern computing systems. From its inception to its evolution into PCI Express, PCI has been a game-changer in device connectivity and communication standards. By adhering to stringent specifications and standards, PCI has proven to be a reliable backbone for diverse hardware configurations, ensuring interoperability and efficiency in the digital age. Comment here.

Read More – >>> How BIOS Works